半导体陶瓷电容器

(1)表面层陶瓷电容器 电容器的微小型化,即电容器在尽可能小的体积内获得尽可能大的容量,这是电容器发展的趋向之一。对于分离电容器组件来说,微小型化的基本途径有两个:①使介质材料的介电常数尽可能提高;②使介质层的厚度尽可能减薄。在陶瓷材料中,铁电陶瓷的介电常数很高,但是用铁电陶瓷制造普通铁电陶瓷电容器时,陶瓷介质很难做得很薄。首先是由于铁电陶瓷的强度低,较薄时容易碎裂,难于进行实际生产操作,其次,陶瓷介质很薄时易于造成各种各样的组织缺陷,生产工艺难度很大。

表面层陶瓷电容器是用BaTiO3等半导体陶瓷的表面上形成的很薄的绝缘层作为介质层,而半导体陶瓷本身可视为电介质的串联回路。表面层陶瓷电容器的绝缘性表面层厚度,视形成方式和条件不同,波动于0.01~100μm之间。这样既利用了铁电陶瓷的很高的介电常数,又有效地减薄了介质层厚度,是制备微小型陶瓷电容器一个行之有效的方案。 [1]

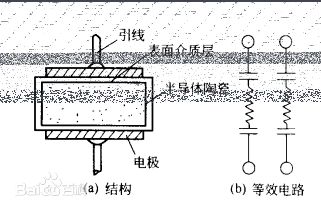

右图(a)为表面屡陶瓷电容器的一般结构,(b)为其等效电路。在半导体陶瓷表面形

表面层陶瓷电容器的结构及其等效电路成表面介质层的方法很多,这里仅作简单介绍。在BaTiO3导体陶瓷的两个平行平面上烧渗银电极,银电极和半导体陶瓷的接触介面就会形成极薄的阻挡层。由于Ag是一种电子逸出功较大的金属,所以在电场作用下,BaTiO3导体陶瓷与Ag电极的接触介面上就会出现缺乏电子的阻挡层,而阻挡层本身存在着空间电荷极化,即介面极化。这样半导体陶瓷与Ag电极之间的这种阻挡层就构成了实际上的介质层。

表面层陶瓷电容器的结构及其等效电路成表面介质层的方法很多,这里仅作简单介绍。在BaTiO3导体陶瓷的两个平行平面上烧渗银电极,银电极和半导体陶瓷的接触介面就会形成极薄的阻挡层。由于Ag是一种电子逸出功较大的金属,所以在电场作用下,BaTiO3导体陶瓷与Ag电极的接触介面上就会出现缺乏电子的阻挡层,而阻挡层本身存在着空间电荷极化,即介面极化。这样半导体陶瓷与Ag电极之间的这种阻挡层就构成了实际上的介质层。

这种电容器瓷件,先在大气气氛中烧成,然后在还原气氛中强制还原半导化,再在氧化气氛中把表面层重新氧化成绝缘性的介质层。再氧化层的厚度应控制适当。若氧化膜太薄,电极和陶瓷间仍可呈现pn结的整流特性,绝缘电阻和耐电强度都得不到改善。随着厚度的逐渐增加,pn结的整流特性消失,绝缘电阻提高,对直流偏压的依存性降低。但是,再氧化的时间不宜过长,否则可能导致陶瓷内部重新再氧化而使电容器的容量降低。还原处理的温度为800~1200℃,再氧化处理的温度为500~900℃。经还原处理后的陶瓷材料,绝缘电阻率可降至10~103Ω·cm,表面层的电阻率低于内部瓷体的电阻率;薄瓷片的电阻率,一般比处理条件相同的较厚瓷体的电阻率低一些。由于再氧化处理形成的表面绝缘性介质层的厚度比较薄,所以尽管其介电常数不一定很高,但是经还原再氧化处理后,该表面层半导体陶瓷电容器的单位面积容量仍可达0.05~0.06μF/cm2。

(2)晶界层陶瓷电容器 晶粒发育比较充分的BaTiO3半导体陶瓷的表面上,涂覆适当的金属氧化物(例如CuO或Cu2O、MnO2、Bi2O3、Tl2O3等),在适当温度下,于氧化条件下进行热处理,涂覆的氧化物将与BaTiO3形成低共溶液相,沿开口气孔和晶界迅速扩散渗透到陶瓷内部,在晶界上形成一层薄薄的固溶体绝缘层。这种薄薄的固溶体绝缘层的电阻率很高(可达1012~1013Ω·cm),尽管陶瓷的晶粒内部仍为半导体,但是整个陶瓷体表现为显介电常数高达2×104到8×104的绝缘体介质。用这种瓷制备的电容器称为晶界层陶瓷电容器(boundarg layer ceramic capacitor),简称BL电容器。 [1]

高压陶瓷电容器

(一)概述

随着电子工业的高速发展,迫切要求开发击穿电压高、损耗小、体积小、可靠性高的高压陶瓷电容器。近20多年来,国内外研制成功的高压陶瓷电容器已经广泛应用于电力系统、激光电源、磁带录像机、彩电、电子显微镜、复印机、办公自动化设备、宇航、导弹、航海等方面。

高压陶瓷电容器的瓷料主要有钛酸钡基和钛酸锶基两大类。

钛酸钡基陶瓷材料具有介电系数高、交流耐压特性较好的优点,但也有电容变化率随介质温度升高、绝缘电阻下降等缺点。

钛酸锶晶体的居里温度为-250℃,在常温下为立方晶系钙钛矿结构,是顺电体,不存在自发极化现象,在高电压下钛酸锶基陶瓷材料的介电系数变化小,tgδ及电容变化率小,这些优点使其作为高压电容器介质是十分有利的。

- 全部产品分类

-

-

嵌入式 - FPGA(现场可编程门阵列)嵌入式 - CPLD(复杂可编程逻辑器件)嵌入式 - 微控制器存储器线性 - 放大器 - 仪表,运算放大器,缓冲器放大器接口 - 模拟开关,多路复用器,多路分解器时钟/计时 - 实时时钟逻辑 - 缓冲器,驱动器,接收器,收发器嵌入式 - FPGA(现场可编程门阵列)嵌入式 - CPLD(复杂可编程逻辑器件)嵌入式 - 微控制器存储器线性 - 放大器 - 仪表,运算放大器,缓冲器放大器接口 - 模拟开关,多路复用器,多路分解器时钟/计时 - 实时时钟逻辑 - 缓冲器,驱动器,接收器,收发器PMIC - 监控器PMIC - 稳压器 - DC DC 开关稳压器时钟/计时 - 可编程计时器和振荡器接口 - 驱动器,接收器,收发器逻辑 - 比较器线性 - 比较器接口 - 控制器存储器 - 控制器PMIC - AC-DC 转换器,离线开关PMIC - LED 驱动器PMIC - 电压基准PMIC - Battery ChargersPMIC - OR 控制器,理想二极管PMIC - PFC(功率因数修正)PMIC - RMS 至 DC 转换器PMIC - V/F 和 F/V 转换器PMIC - 以太网供电(PoE) 控制器PMIC - 全,半桥驱动器PMIC - 显示器驱动器PMIC - 栅极驱动器PMIC - 激光驱动器PMIC - 热插拔控制器PMIC - 热管理PMIC - 照明,镇流器控制器PMIC - 电机驱动器,控制器PMIC - 电池管理PMIC - 电源控制器,监视器PMIC - 电源管理 - 专用PMIC - 稳压器 - DC DC 切换控制器PMIC - 稳压器 - 专用型PMIC - 稳压器 - 线性PMIC - 稳压器 - 线性 + 切换式PMIC - 稳压器 - 线性晶体管驱动器PMIC - 稳流/电流管理PMIC - 能量测量PMIC - 配电开关,负载驱动器RF 收发器 IC专用 IC存储器 - 用于 FPGA 的配置 PROM嵌入式 - DSP(数字式信号处理器)嵌入式 - PLD(可编程逻辑器件)嵌入式 - 微控制器 - 应用特定嵌入式 - 微控制器或微处理器模块嵌入式 - 带有微控制器的 FPGA(现场可编程门阵列)嵌入式 - 微处理器嵌入式 - 片上系统 (SoC)接口 - I/O 扩展器接口 - UART(通用异步接收器/发送器)接口 - 专用接口 - 串行器,解串行器接口 - 传感器和探测器接口接口 - 信号终端器接口 - 信号缓冲器,中继器,分配器接口 - 模块接口 - 模拟开关 - 专用接口 - 滤波器 - 有源接口 - 电信接口 - 直接数字合成(DDS)接口 - 编码器,解码器,转换器接口 - 编解码器接口 - 语音录制和重放接口 - 调制解调器 - IC 和模块数据采集 - ADCs/DAC - 专用型数据采集 - 数字电位器数据采集 - 数模转换器数据采集 - 模数转换器数据采集 - 模拟前端(AFE)数据采集 - 触摸屏控制器时钟/计时 - IC 电池时钟/计时 - 专用时钟/计时 - 延迟线时钟/计时 - 时钟发生器,PLL,频率合成器时钟/计时 - 时钟缓冲器,驱动器线性 - 放大器 - 专用线性 - 放大器 - 视频放大器和频缓冲器线性 - 模拟乘法器,除法器线性 - 视频处理线性 - 音頻放大器逻辑 - FIFO 存储器逻辑 - 专用逻辑逻辑 - 信号开关,多路复用器,解码器逻辑 - 多频振荡器逻辑 - 奇偶校验发生器和校验器逻辑 - 栅极和逆变器逻辑 - 栅极和逆变器 - 多功能,可配置逻辑 - 移位寄存器逻辑 - 触发器逻辑 - 通用总线函数逻辑 - 锁销逻辑 -计数器,除法器逻辑器件 - 转换器,电平移位器

-

-

用户评论